公共篇:

本周,我们实习生有幸受到邀请,和实验室里的其他同学一起到Jim教授家吃饭。早就听闻Jim家藏在在深林之中,有机会得此一见,确实不枉此行。晚宴非常丰富,有水果和饮料,还有美味可口的中国菜!

吃过晚饭过后,我们一起来到Jim家后院(超级大),给他们家的宠物草泥马(羊驼)喂食。草地上排列着接近20只草泥马,场景颇为壮观。话不多说,直接上图:

个人篇:

朱世达

这周开始进入收尾阶段,首先是理清楚项目的思路和未来的方向。关于absorbing material research,我们的目的不是找到新的characterization的方法,而是研究material的性质,所以我们首要的是对NS1000材料的这种特殊性质进行研究。Microstrip line method characterization虽然值得研究,而且适合发paper,但是只能放在次要位置。

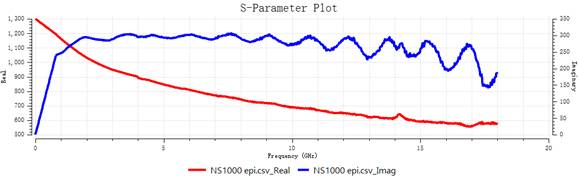

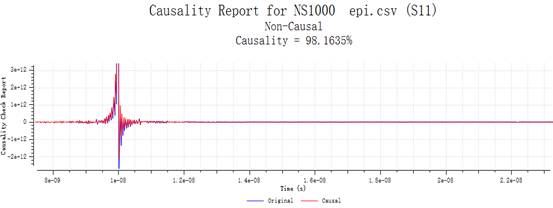

针对NS1000超高的epi,Jim让我确认一下测试数据的causality,我先是测试了S参数的causality,但是Jim希望直接测试材料epi的causality,这个在软件上不能直接实现。我们求助过Michael以后,用MATLAB把epi的数据用两段直线延长了曲线,增加了低频部分的数据,并在频域上乘以一个

,相当于在时域上进行了一个平移,然后调整了时域的单位,最后验证的结果是测试的causality达到了要求。

,相当于在时域上进行了一个平移,然后调整了时域的单位,最后验证的结果是测试的causality达到了要求。

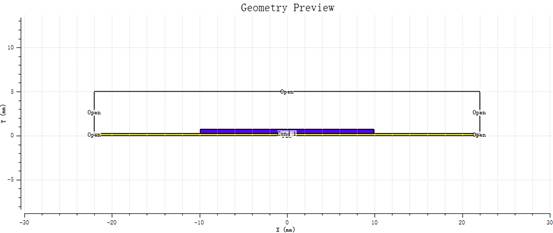

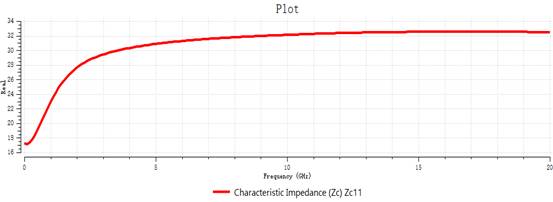

另外我们在截面上进行了2DFEM的仿真,并查看了特征阻抗的变化。

相比于以前的仿真结果,首先这个特征阻抗不是恒定的,因为测试的是覆盖吸波材料的区域,而不是CST仿真的PORT处的特征阻抗。另外这个结果和TDR测试的结果也不对应,现在还不是很清楚TDR测出的20Ohm阻抗是代表了什么。但是这里验证了我们在算法中对Z的描述,是针对频率变化的。

我想继续研究算法还是可以从2DFEM代码和GA算法结合,找到匹配最优解,这应该是进一步的研究方向。

关于Optical RF的项目,我们的目的是做出产品,第一个产品已经给Apple寄过去了,第二个是需要寄给BOSCH的,并且我们希望可以做到10G。这一周板子都没有寄到,所以下周我们才有机会去装配。检查了一下需要的部件,所有材料都已经准备齐全了,就是差一些长光纤。我们在网上找了半天才找到合适的产品,英文叫做LC-LC 62.5/125um simplex fiber optical patch。结果找到的最合适的一家竟然又是从中国发货的,这样一来,运费就会非常昂贵。实验室最近邮费管得特别严,不允许邮费比产品费贵。但有意思的是,其他厂家的产品贵得多,比中国这一家的产品费加上邮费还要贵。我和小帕争论了半天,最后周末的时候小帕还是决定不从中国买,原因是return policy不符合实验室的规定。不过,我和这个厂家的美国营销部门的交流很愉快,对方发了几封邮件来和我沟通,并且表示尊重我们实验室的规定。

欧阳沐齐

这周是这个暑期实习的倒数第二周,整个实习已经基本上接近尾声,我的工作也进入了最后的收尾阶段。

在上周,我的主要任务是重新设计USB Type-C中的PCB,使得传输线能够达到更好的性能指标。这一周,我也没有其他新的任务,需要做的就是对之前设计的PCB进行进一步的修改。

第一次修改,我面对的主要问题是如何将PCB的面积进一步减小。因为在最后的产品中,这个PCB是需要放入传输线中的,过大的面积会造成传输线体积的增加,增加生产成本和空间,降低实用性。虽然我需要减小的尺寸不是很多,但是有很多器件的布局都需要重新设计,因此我选择了直接新建一个PCB全部重新布局,这样调整起来反而更加方便一些,还有原来的版本可以作为一定的参考,方便在做调整的时候能够有一点依据。

第二次修改,难度与第一次相比更大。因为PCB的面积有限,并且是多层的PCB,所以在之前的设计中,我通过很多过孔来连接各层之间的信号和电源,包括了通孔和盲孔。但是后来了解到采用盲孔的话,会在很大程度上增加PCB的生产成本,因此在这个设计中只能够采用通孔来完成各层之间的连接,这对减小PCB的面积更加的不利。因为之前采用盲孔的设计,在同一个位置,可以用盲孔连接到下一层的地电位,同时还可以从反面来连接Vcc电位。除此之外,PCB上有些元件需要通过机器来焊接,这样的话如果在焊盘下增加过孔,可能会导致虚焊,需要补焊锡,又为了能够节约较多的空间,因此只能在可以手焊的焊盘上叠加上过孔来减小整个PCB设计需要的面积。

在减小面积的同时,设计PCB的时候还需要考虑到在信号频率非常高的情况下仍然能够保证正常的工作,这方面的设计需要一定的经验积累,我只能讲自己的设计结果给其他人检查,然后根据他们的意见再进行一定的调整,以获得更好的效果。

杜航

前一阶段connector tapering做了一系列的仿真,也得到了一些结果。本周我的主要精力都集中在wire bonding上面。

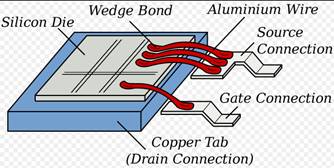

什么是wire bonding?

Wire bonding is the method of making interconnections between an integrated circuit (IC) or other semiconductor deviceand its packaging during semiconductor device fabrication.

由于wire bonding会导致连接处的感性增加,造成该处的阻抗不匹配,所以我要做的是尽量优化设计,使得wire bonding引起的阻抗匹配尽量小。因此我需要让wire bonding的loop尽量小。

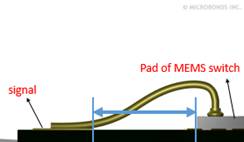

在我正在做的MEM switch项目中,需要把signal和MEM switch的pad进行wire bonding。

Wire bonding的几种材料有什么利弊呢?

主流的有两种材料,金和铜。铜的好处在于成本远低于金,金的好处在于金线的直径最大可以做到76um,但是铜线最大只能做到25um。线的直径越大,就更能够减小wire bonding的感性。

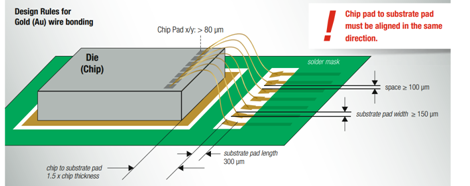

Design rule

上图给出了水平方向的gap一般设计为die厚度的1.5倍。但是因为在我想让wire bonding的loop尽量小,所以我需要gap越小越好。上一版中用到的距离是0.3mm。根据我在网上找到的资料,这个gap是可以更小的。但是具体的可能还要和manufacturer确认。

为了使得loop小,有三种优化方案:

1.gap尽量小(上面已经提到)

2.使得MEMS switch和PCB在同一个平面上。上一版也是这样设计的,但是因为MEMS switch的datasheet上面的尺寸有问题,导致后来两个部件依然不在同一个平面。所以这一次我需要有一些关于MEMS switch的尺寸的测量结果。

3.使用两到三根wire进行bonding。(需要仿真确认)

陈达

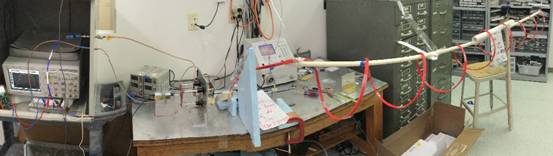

上周末的时候小帕去加州参加了一个EMC的会议,所以这周和Panasonic的会议只有我和Jeet向公司做presentation。会议上主要还是讲我在T-Model上面的一些探索,在进一步确立了T-Model的可行性后,下一步我们计划去用实际的Buck converter和transmission line去搭建一个setup,做一些measurement和仿真值比较。做这些主要还是铺垫作用,为了以后能在EMCoS里面能够应用T-Model,所以光是仿真还是不够的。

Bosch方面,我们做了一些改进,我们在原来的基础上,又将示波器直接连接在PC机上,然后在PC机上用matlab通过com口发送一个指令给Arduino,控制characterization board上的不同relay,然后示波器自动地测量current probe的电流和voltage probe的电压,将测量到的数据传送给PC机,matlab再对传回的数据处理,进行FFT变换,并通过程序算出source Model。全部过程只需要你在matlab里面输入几个数字(分别代表不同relay)即可,非常简单方便,简化了实验过程。

(实验的setup)

另外,这周六,实验室的教授Jim邀请了他的学生和我们实习生去他家吃晚餐。Jim的家非常大,还有一大片草场养着19只憨态可掬的羊驼。吃完饭大家一起坐在客厅聊天,整个晚餐氛围都很好。

(Jim家的草场和羊驼)

靳航

这一周是我们在罗拉的倒数第二周,也是我们在异国他乡度过的第一个中秋节。我们也吃到了饺子和月饼!Jim教授这周邀请我们去他家吃晚饭。在他家里,我们看到了Jim养的神兽草泥马,还喂了它们。Jim还养了一只4个月大的kitty和一只13岁的狗。总得来说,我愉快地度过了这一周。

(饺子和月饼)

(Jim家养的草泥马)

(猫和狗)

这周,小帕去加州开会,他把一些重要的事情在上周交代给我了,所以我做得挺顺利,将新的structure做了measurement和simulation,结果显示还不错,最后的工作也做完了,就只剩下所有的数据分析了。

(新搭的structure)

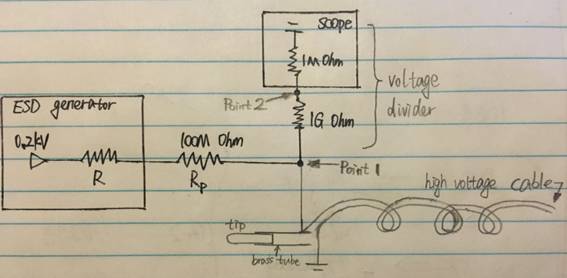

(自己做了个Voltage divider检查保护电阻是否有过大)